- 全部

- 默认排序

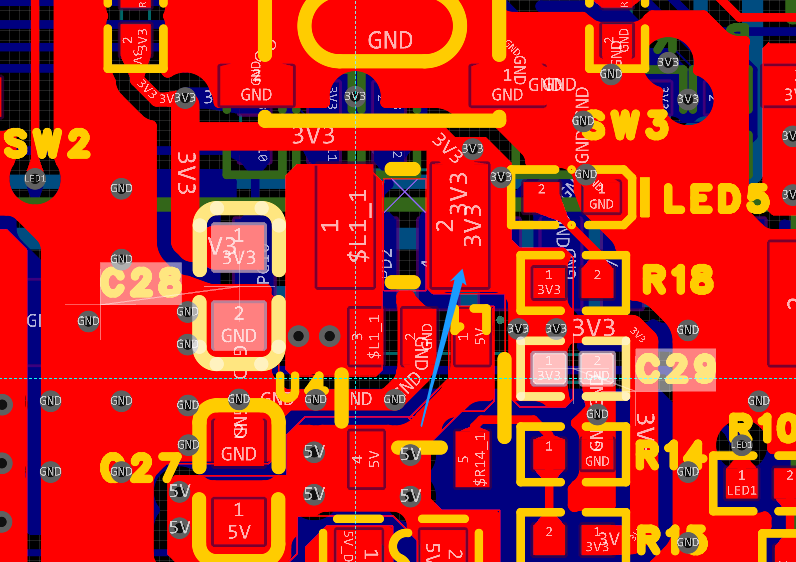

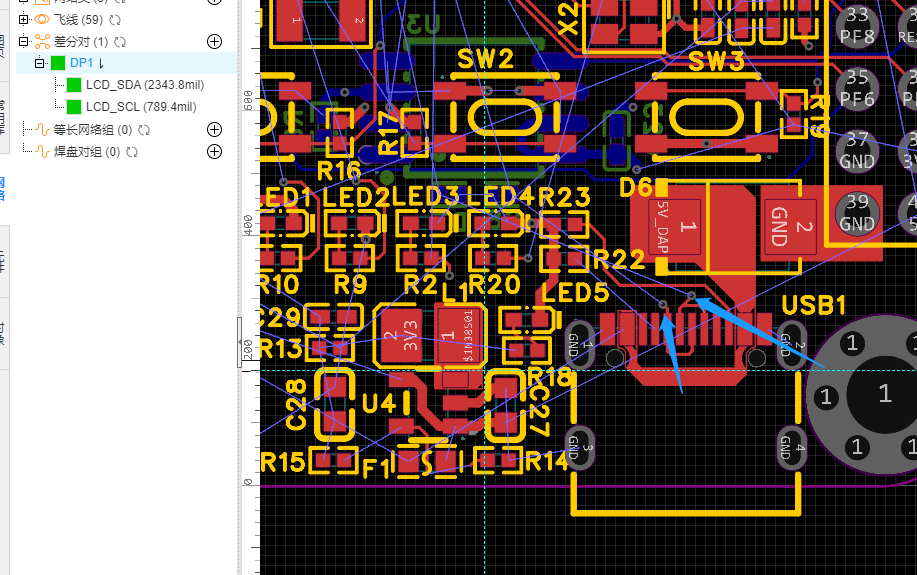

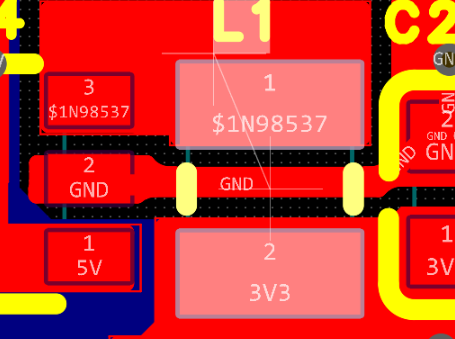

1.电源输入的滤波电容应该靠近输入管脚(4脚)放置2.差分走线要尽量耦合出线,满足差分间距规则3.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-FPC1)4.器件摆放尽量对齐处理5.pcb上存在开路现象6

电源输出的滤波电容要靠近输出管脚放置2.USB的电容放置不到位,应该线经过电容在连接到USB器件,差分出线要耦合出线,走在一起3.器件干涉4.SDRAM的滤波电容尽量保证一个管脚一个5.顶底层器件干涉,顶层器件是插件,你底层也放器件,后期不

USB信号需要创建差分对2.电源输入的滤波电容应该靠近输入管脚(4脚)放置3.优先晶振走线,靠近IC放置,走类差分形式,并包地处理,晶振下面不要走线4.器件摆放尽量对齐处理后期把线连通,等长完后在进行评审

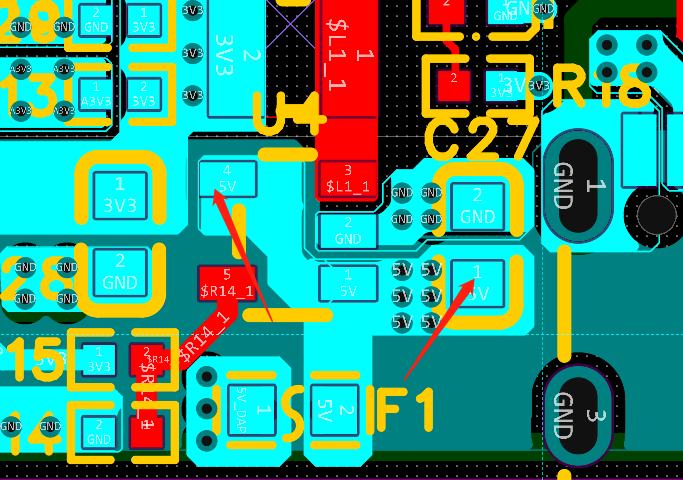

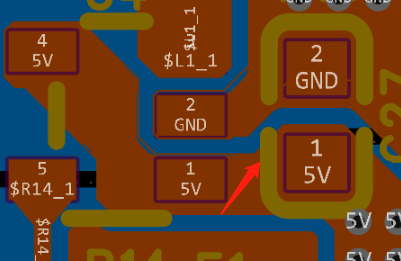

电源模块反馈电路错误,r15接入反馈电源到r14在到5号管脚。2.晶振布局布线错误3.typec差分对内误差控制5mil以内,尽量避免出现不耦合4.TF卡所有信号线要整组 ,做等长处理以时钟线为目标,目标控制在300mil以内。

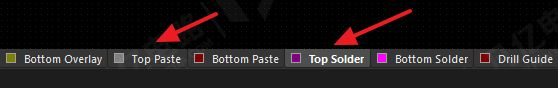

大家在绘制PCB的时候会发现我们的EDA软件当中都存在阻焊层和钢网层这两个层,那么大家有想过这两个层是有什么作用呢?注意:阅读之前,请大家先理解下PCB两个不同的概念,阻焊层与阻焊阻焊层的作用:就是防止不该被焊上的部分被焊锡连接,一般说的是

大家学习完我们上一期的阻焊与阻焊层的介绍之后,相信大家对此也有一定的了解了,那么我们这期给大家介绍一下什么是PCB钢网!首先我们先看一下钢网层在EDA软件上面的表现形式:大家会发现,在钢网层当中有一些器件是有钢网的,有一些是没有钢网的,我们

这周让我们从繁杂的模电学习中逃离出来,看看占据中国EDA30%市场份额的巨头公司Cadence带来的原理图仿真工具PSpice的应用。开设新版块的原因 小电最近在给Cadence公司的官方公众号写PCB产品线中原理图仿真部分的教程,感觉不管是针对刚刚开始接触模拟电路的同学,还是已经工作的小

随着单片单片器件上集成的功能越来越多,高密度微孔已成为集成系统等硬件技术的应用,自由角度布线和自动布局布线等开始成为EDA工具的必备功能,然而很多小白不太清楚自动布线和自由角度布线是什么?有什么用?今天安排!1、设计约束条件由于要考虑电磁兼

扫码关注

扫码关注